Analogā-digitālā pārveidotājs - mērķis, klasifikācija un darbības princips

Elektroniska ierīce, ko sauc par analogo-digitālo pārveidotāju (ADC), tiek izmantota, lai pārveidotu analogo signālu ciparu signālā (lasāmā binārā koda tipa secībā). Analogā signāla pārveidošanas procesā ciparu formātā tiek īstenota: paraugu ņemšana, kvantēšana un kodēšana.

Paraugu ņemšana tiek saprasta kā paraugu ņemšana no nepārtraukta analogā signāla atsevišķām (diskrētām) vērtībām, kas krīt laika momentos, kas saistīti ar noteiktiem pulksteņa signālu intervāliem un ilgumiem, kas seko viens otram.

Kvantēšana ietver paraugu ņemšanas laikā atlasītā analogā signāla vērtības noapaļošanu līdz tuvākajam kvantēšanas līmenim, un kvantēšanas līmeņiem ir savs kārtas numurs, un šie līmeņi atšķiras viens no otra ar fiksētu delta vērtību, kas ir nekas vairāk kā kvantēšanas solis.

Stingri sakot, paraugu ņemšana ir process, kurā tiek attēlota nepārtraukta funkcija kā diskrētu vērtību virkne, un kvantēšana ir signāla (vērtību) sadalīšana līmeņos. Runājot par kodēšanu, šeit kodēšana tiek saprasta kā kvantēšanas rezultātā iegūto elementu salīdzinājums ar iepriekš noteiktu kodu kombināciju.

Ir daudzas metodes, kā pārveidot spriegumu kodā. Turklāt katrai no metodēm ir individuālas īpašības: precizitāte, ātrums, sarežģītība. Atbilstoši konversijas metodes veidam ADC iedala trīs grupās

-

paralēli

-

konsekvents,

-

seriāli-paralēli.

Katrai metodei signāla pārveidošanas process laika gaitā notiek savā veidā, tāpēc arī nosaukums. Atšķirības slēpjas tajā, kā tiek veikta kvantēšana un kodēšana: seriālā, paralēlā vai seriāli paralēlā procedūra, lai tuvinātu digitālo rezultātu pārveidotajam signālam.

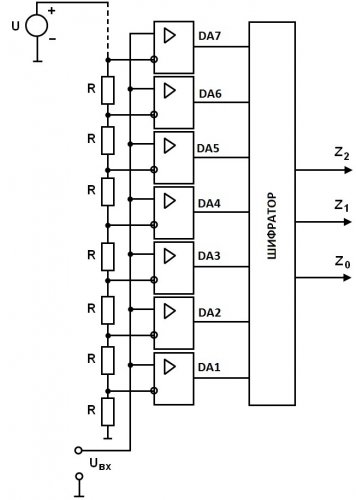

Paralēlā analogā-digitālā pārveidotāja diagramma ir parādīta attēlā. Paralēlie ADC ir ātrākie analogo-ciparu pārveidotāji.

Elektronisko salīdzināšanas ierīču skaits (kopējais DA komparatoru skaits) atbilst ADC kapacitātei: diviem bitiem pietiek ar trim, trīs - septiņiem, četriem - 15 utt. Rezistora sprieguma dalītājs ir paredzēts, lai iestatītu pastāvīgu atsauces spriegumu diapazonu.

Ieejas spriegums (šeit tiek mērīta šī ieejas sprieguma vērtība) vienlaikus tiek pielietots visu komparatoru ieejām un salīdzināts ar visiem atsauces spriegumiem tiem, kurus šis pretestības dalītājs ļauj iegūt.

Tie salīdzinātāji, kuru neinvertējošās ieejas tiek barotas ar spriegumu, kas ir lielāks par atsauci (ko dalītājs pieliek invertējošajai ieejai), izejā dos loģisko, pārējos (kur ieejas spriegums ir mazāks par atsauci vai vienāds ar nulle) iedeva nulli.

Pēc tam tiek pieslēgts kodētājs, kura uzdevums ir vieninieku un nulles kombināciju pārvērst par standarta, adekvāti saprotamu bināro kodu.

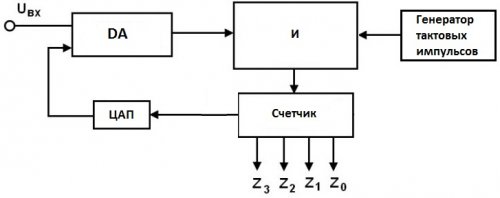

ADC shēmas seriālajai pārveidei ir mazāk ātras nekā paralēlo pārveidotāju shēmas, taču tām ir vienkāršāks elementārs dizains.Tā izmanto salīdzinājumu, UN loģiku, pulksteni, skaitītāju un ciparu-analogu pārveidotāju.

Attēlā parādīta šāda ADC diagramma. Piemēram, ja izmērītais spriegums, kas tiek pievadīts salīdzinājuma ķēdes ieejai, ir lielāks par otrās ieejas (atsauces) rampas signālu, skaitītājs skaita pulksteņa ģeneratora impulsus. Izrādās, ka izmērītais spriegums ir proporcionāls saskaitīto impulsu skaitam.

Ir arī sērijveida paralēlie ADC, kur analogā signāla pārveidošanas process ciparu signālā ir atdalīts telpā, tāpēc izrādās, ka maksimālais kompromisa ātrums tiek sasniegts ar minimālu sarežģītību.